614.4×8×15/(10×16×3.84)/(20+20)=3

因此,在多载波系统中,可以选择用一条CPRI链路来传输多载波I/Q数据,或是通过多条CPRI链路分别传送不同载波的数据。

超帧单元是由256个基本帧单元构成的,其中,第1个基本帧单元里的控制信号写入K28.5特殊字用标志一帧的开始,K28.5是8B/10B里的特殊控制字。其余的255个基本帧单元里的控制信号按规定顺序分别填入帧号、基站帧号、版本号、控制管理字、HDLC、厂商特定字,并留出了一些做为保留字节。

通过适当的网络协议,可以使用基带处理和射频拉远设备的级联、星形、树形和环形的组网方式,而具体采用何种网络协议,则由厂商自己决定。

公共无线接口规范的FPGA实现

在公共无线接口规范的实现中,最关键的一环是千兆比特收发器的实现和串/并、并/串转换器(SEDES)的实现。在当前主流的FPGA中,Alter、Xilinx均将千兆比特收发器和SEDES硬件电路集成到了FPGA芯片中,像Altera的StratixGX系列FPGA可以提供4路~20路的高速串行收发器接口,每个接口支持的最高速率可达3.1875Gb/s,并支持全双工。CPRI链路的最高速率为2.4576Gb/s,因此,本文讨论的方案就是在StratixGX芯片上实现公共无线接口规范。本系统涉及到的时钟较多,多时钟系统会引起时钟速率抖动和时钟/数据关系相位变化,甚至毛刺会严重降低设计性能或完全破坏设计所能实现的功能,并对高速串口造成致命的影响,因此,对于多时钟系统的设计应尽量减少亚稳态状态的产生。下面分模块进行讨论:

(1)可调节的时钟模块的实现。由于信道最多支持三种数据码率,在初始上电时码率需要进行协商并能自动调节。在StratixGX里有增强型锁相环(EPLL)和快速锁相环(FastPLL),由EPLL的分频和倍频可以从输入的低速时钟产生高速的系统工作时钟。GX里还提供了可动态实时重配置EPLL的IP核,因此,可以通过改变其控制寄存器的值,来实时重新配置EPLL,以得到不同的系统工作时钟。

(2)开机初始化模块的实现。由于发送端和接收端开机初始时的工作时钟不一定相同,因此需要通过初始化达到统一的工作时钟,并确定物理层的传输速率和相应的协议。

(3)I/Q用户数据和链路层数据的码率调整模块实现。进入基带处理部分的I/Q数据是3.84M或3.84M的倍数速率,需要通过二端口异步RAM,一端在低速时钟下写入RAM,另一端在高速时钟下从RAM中读取数据至成帧模块。

(4)8B/10B编解码和成帧/解帧模块的实现。该模块的实现是通过GX里的GXB(GigabitTransceiverBblock)集成电路模块来完成的。

(5)接收端时钟的恢复模块的实现。由于在高速串行数字接口中,时钟信息和数据信息是叠加在一起的,保持接收端和发送端的时钟同步,并从数据信息中提取出时钟信号是接收端正常工作的关键。在GXB模块里,有时钟数据恢复单元(CRU),CRU用外部参考时钟从进入的数据信号里恢复出它的时钟,并且该时钟和数据是同相位的。恢复出来的时钟即用做接收端的系统工作时钟,进行下一步的数据处理。

高速数字信号传输的仿真

在硬件实现中,数字信号在614.4Mb/s、1228.8Mb/s、2457.6Mb/s三种码率之一下的传输质量将会受到很多因素的影响,设计人员很难保证一次性成功,必须在设计硬件前进行全面的系统级仿真,然后再去布板调试改善。充分利用分析工具来实现准确的性能预测是提高高速产品设计质量的关键所在。

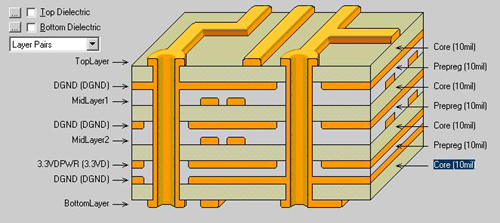

对StratixGX进行布板时,为了保证较好的性能,现用图5的8层布板方案来进行仿真。高速传输线采用差分信号线,从顶层经过孔到第五层,再通过过孔到顶层。该走线经历了两次过孔和两次45度拐角。

图5八层布板方案

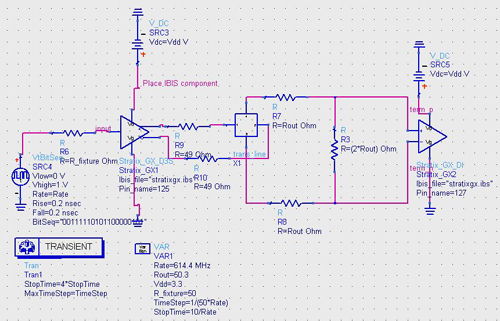

发送端和接收端均采用3.3V低电压差分接口(LVDS),altera提供了LVDS的输入输出缓冲模型(IBIS),该模型属于形为级描述模型,它包含了输入输出缓冲的I-V数据和V-T数据,包括了上升沿下降沿。IBIS模型可以用来进行PCB上信号完整性分析,还可以进行某些算法分析,比如预加重或者均衡。

差分信号到达开路终端后,将会碰到一个很大的阻抗并反射回来,如果不对此反射加以控制,它将可能超出噪声容限引起超额噪声。减小反射的一种常用办法就是在差分对末端加上一个与差分阻抗匹配的电阻性阻抗。用ADS仿真出LVDS的输出阻抗,加入串联终端匹配,再仿真出输出缓冲模型和信道模型的综合模型的输出阻抗,对接入匹配的端接电阻进行系统仿真,测试序列为K28.5(0011111010),优化后的系统框图如图6所示:

图6系统仿真框图

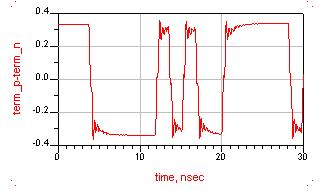

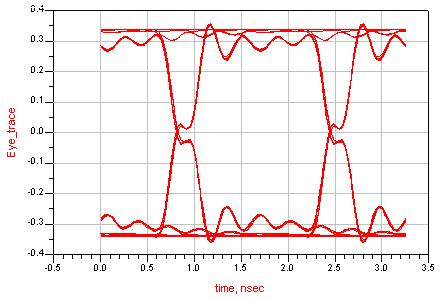

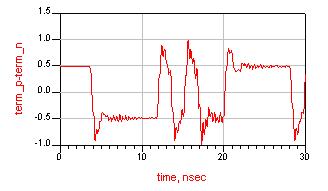

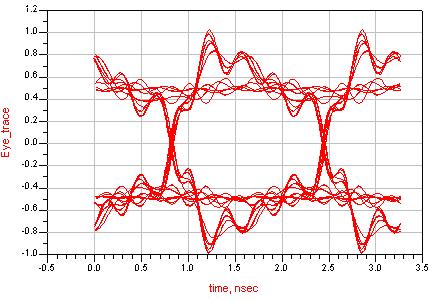

优化后的差分电压时域仿真波形图如图7所示,差分电压眼图如图8所示,和未优化前进行比较,如图9、图10所示,从对比可知,加了终端匹配和端接匹配后,过冲现象有较大改善,但是接收电平值有所下降,信号眼图略微收缩,即系统的抗干扰能力有一定的下降。

图7差分电压时域仿真波形

图8差分电压仿真眼图

图9未匹配的差分电压时域仿真波形图

图10未匹配的差分电压仿真眼图

结论

基带处理和射频拉远两部分设备之间的标准化接口是有效实现控制与数据传输的保证,可以为运营商节约成本、加速网络建设、提高网络容量,按照固定的成帧解帧方式的标准化设计有利于不同产品间的兼容。