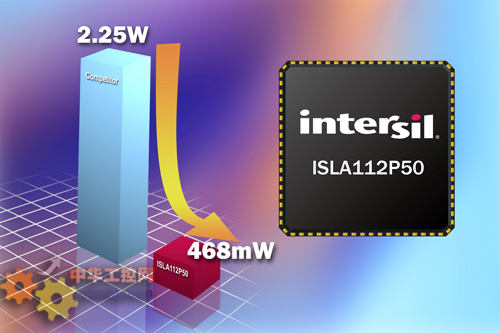

Intersil公司今天宣布, 推出全新 8 位、10 位、12 位 500MSPS 模数转换器系列。12 位的ISLA112P50 IRZ 500MSPS 模数转换器作为该系列的领衔产品,其功耗仅为 468 毫瓦,比所有12 位 500MSPS ADC 同类竞争产品都低 5 倍。

由于在采用ISLA112P50后,系统功耗会大幅降低,因此系统设计人员能够在单个系统中集成多个 ADC,而且不会出现高性能 ADC 常见的散热问题。此外,ISLA112P50 的低功耗还能够在不影响性能的情况下有助于延长电池使用寿命,从而让便携式或电池供电应用领域的设计人员受益匪浅。

ISLA112P50 是 Intersil不断扩展的高性能、低功耗 ADC 系列中的最新产品,采用了 Intersil 标准 CMOS 工艺的专有 FemtoCharge 技术,并专门针对宽带通信、雷达、激光探测及测距系统 (LIDAR) 以及数据采集系统而开发。ISLA112P50 采用一对时序交错式 250MSPS 单元 A/D 生成 500MSPS 的采样率。此外,该款 IC 还采用了 Intersil Interleave Engine (I2E) 专利技术,可对偏移、增益以及单元 A/D 之间采样时间失配进行自动精密校正以确保高性能。

该模数转换器的动态性能与规范是高端数据采集系统等目标应用的最佳选择。模拟输入带宽为 1.15GHz。输入频率为 190MHz 时,信噪比为 65.8dBFS,SFDR 为 80dBc。该产品还融合了打盹/休眠模式,数字输出数据采用 LVDS 或 CMOS 格式,从而提高了设计灵活性。

同步时钟分频器复位协助多器件的时间校准,支持板级交错或同步采样,这对某些系统而言是一项非常重要的特性。A/D 输入时钟指定的最小/最大接口时序可以使设计人员收敛时序,并选择性价比最高的 FPGA 来满足时序要求,从而提高系统可靠性。

此外,ISLA112P50 还能用串行外设接口端口进行轻松配置,其能控制交错式校正电路,进而让系统发出持续的校准命令并配置动态参数。

12 位 ISLA112P50 也是引脚兼容的转换器系列中的一员,该系列产品包括 10 位ISLA110P50 和 8 位 ISLA118P50。这些产品均采用仅为 10x10mm 的小型 72 引脚 QFN 封装,与同类竞争产品相比,封装尺寸缩减了 49% 到 77%。

提供灵活的评估系统

Intersil 还推出了业界最灵活的评估系统,该系统旨在帮助设计人员分析时域和频域的性能。系统采用模块化设计,用一个主板支持多个 ADC 系列。Matlab 代码适用于硬件在环分析,并能够一次连续捕获超过 100 万个采样。用户可将捕获数据下载到标准的 CSV 文件中,并采用专门的后处理技术。