全球消费类视频应用正在进入一个令人兴奋的新阶段。传统的视频内容只提供有限的商业电视节目以及电影或与个人录像节目等。如今,视频内容的选择种类大幅增加,而且获得视频内容的途径也变得多种多样:互联网、共享媒体、地面及卫星广播、IP广播、手机、视频点播、新媒体格式以及P2P传输等。

消费者可以通过很多的方法获得视频内容,但是,由于终端产品播放能力的限制,不能使消费者享受全部新形式的视频内容。原本能促进消费市场应用的半导体器件现在却阻碍了消费者获取多种格式的媒体信息。进一步,为了转移、转码和播放不同格式的视频内容,在播放终端上又增加了外围芯片,如硬盘控制器,闪存卡读取器,DVD控制器等,增加了系统的材料。现实市场需要满足消费者新需求的新解决方案。

为什么播放器需要支持多种视频压缩格式?

消费者应该能随意播放任何格式的内容;播放器应该能不拘格式地自动解码播放。以下根据来源举例说明常见的媒体数据格式:

移动电视:

*广播制式:DVB,DMB,DVB-H,S-TiMi等

*可能采用相对于固定电视的较窄信号带宽,播放预先减采样的QVGA低清晰度内容

*可能采用固定电视及其光缆传播所常用的成熟高清晰MPEG2压缩(例如现行T-DMB的载波内容)

通过网络下载:

*采用H.264的高清电视内容约占10%

*采用RealVideo10,或MPEG4/ASP,D1分辨率,的内容约站80%

*Real与MPEG4比较,例如压缩一个电影,前者可压缩到300MB,后者维600MB

从DVD和有线电视节目取得内容:

*通常为MPEG2

*新兴的IP电视应用,则需要MPEG4或者更高压缩比的算法来满足较低速网络上的应用

个人视频共享:

*时兴新技术和应用,两种常见的制式:

oU-Tube

oFlashVideo(FLV)

WindowsVideoMedia9

*市场上标志性的媒体标准功能

中国自主知识产权的AVS标准

*已经被认可,并正在逐步为国内的内容和运营行业所采用。

当我们最初定义VivaceVSP芯片系列的产品规格时,我们意识到了:无论应用系统是否便携、价位高低、显示屏大小,媒体处理芯片的能力必须能充分实现解码各种媒体压缩格式、保证D1@30fps的实时解码和显示。否则总是要通过PC软件转码才能达到设备之间媒体内容地无缝衔接。

目前便携媒体播放器(或称为MP3.5/MP4)能播放的视频内容

在各种MP3播放器,尤其是苹果公司的高端系列产品和内容服务的带动下,MP3播放器的市场在过去5至7年中增长巨大。视频播放功能成为最吸引消费者的卖点。为此,MP3制造商和ODM供应商竞相寻找在保持低价位前提下、能在MP3播放器中增加视频功能的系统解决方案。幸运的是,闪存和硬盘的部件降价帮助保持了新增视频系统的成本空间。但是,在授权下载和播放的内容从单纯音频到音视内容和电影时,便携DSP在应用上遇到了技术挑战。

2006年,支持有限条件下视频功能的MP3播放器产品开始进入市场。然而,几个不利因素制约了其在市场上流行的势头。关键的障碍是使用者在下载内容之后,仍要在PC上对内容继续进行软件DSP处理。“转码”的过程事实上是“解码-图像下采样-缩小帧幅-重新压缩到便携DSP能力所限制的格式”的长过程。事实上,由于各自媒体压缩标准的不同,根本不可能有所谓的简单“转码”。要转换压缩格式,只有先解压、再压缩。但这种方法并不理想,“转码”存在三方面问题:第一,播放器中的视频处理器没有同时支持多种媒体格式的功能,因此视频内容必须转换为手持设备所能接收的某种格式;第二,播放器中的DSP芯片处理能力达不到D1@30fps的实时解码速度;第三,播放器中的低性能芯片无法对高分辨率内容进行缩小帧尺寸的运算处理,以适应便携式产品的显示分辨率。总之,当前的便携播放器DSP芯片已不能满足消费者所追求的视频体验。

芯慧同用VSP芯片支持的MP4播放器方案

下文介绍VSP媒体处理器系列中的一款新产品:VSP100媒体处理器。VSP100采用专门设计以满足视频市场的需求,尤其适合作为视频协处理器应用。它能实时处理多种数据格式和不同分辨率的视频内容,能缩放内容以适合便携显示的通常分辨率,可延长播放时间,缩短系统产品进入市场的时间,增加视频功能的系统设计成本最低。VSP100芯片特性:

*功耗25~50mW,支持QVGA和H.264标准的媒体解码和播放

*ViViD媒体DSP子系统(图1)运行时钟为125MHz

*RISC通用CPU运行时钟达180MHz

*内部集成的8-16比特的SDRAM/DDR内存控制器

*支持所有主流媒体标准

*高达VGA分辨率的LCD控制器

*在中芯国际以130纳米工艺制造

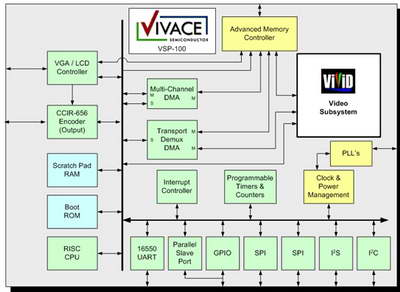

图1给出了VSP100芯片上所集成的主要功能模块。

图1:VSP100SoC架构。(右上角为芯慧专利ViViD多核子系统)

VSP100芯片由多核的ViViD子系统承担视频DSP的工作。如下图所示,它包含了三个定制设计的视频DSP核,每个DSP核又分别配置了针对视频算法加速的定制硬件化宏指令(DDCU)。三核组成流水线操作(码流处理、图像变换和运动补偿),保证在任意时刻都能同时处理在三个不同阶段的解码任务。DSP采用VLIW体系结构,在每个并行运行的数据通道上都能任选一个定制的宏指令加速器来执行。定制宏指令加速器预先编程并硬件化,实现运算功能(如ALU)或视频编解码常用的DSP过程。VSP100能在很低的时钟频率和低功耗下实现高速处理。